# = Preliminary =

# AP4410BEC

# **Ultra Low Power Dual Voltage Detector**

### 1. General Description

The AP4410BEC is a voltage detector IC for monitoring battery, power supply and system voltage. The circuit includes dual voltage detection with built-in gate logic and MOSFETs. The AP4410BEC offers ultra-low power consumption that is 0.026µA per channel.

The built- in CMOS logic circuit can be controlled independently from the voltage detector. The polarity of the voltage detection results is controlled by pins. This function enables the AP4410BEC as a load switch by using the results of the voltage detection. The AP4410BEC achieves better performance and PCB area than conventional CMOS voltage detection ICs, with discrete logics and external MOSFETs. The AP4410BEC is ideal for voltage conversion or load switch of thin and small wearable devices, over charge/discharge protection of Lithium-ion batteries, power management part of energy harvesting applications.

#### 2. Features

Power management function

Dual voltage detection circuits

Control logic with independent power supply

Built in P-channel MOSFETs and N-Channel MOSFETs for each channel

Wide range for detection voltage

Detection voltage "High"

1.8 to 4.4V (Options)

Detection voltage "Low"

1.7 to 4.3V (Options)

• Voltage detection accuracy  $\pm 35 \text{mV}$

Ultra-low power consumption

0.026µA typical/ch. 0.050µA maximum/ ch

Response Speed 500µs maximum

On resistance

On-chip P-channel MOSFETs 1Ω typical

On-chip N-channel MOSFETs 2Ω typical

Operation temperature -40 - 85 °C

Package

20-pin WLCSP (1.955×1.555mm, 0.4mm pitch)

Rev 0.0 - 1 - 2017/12

# 3. Table of Contents

| 1.  | General Description              | 1  |

|-----|----------------------------------|----|

|     | Features                         |    |

| 3.  | Table of Contents                | 2  |

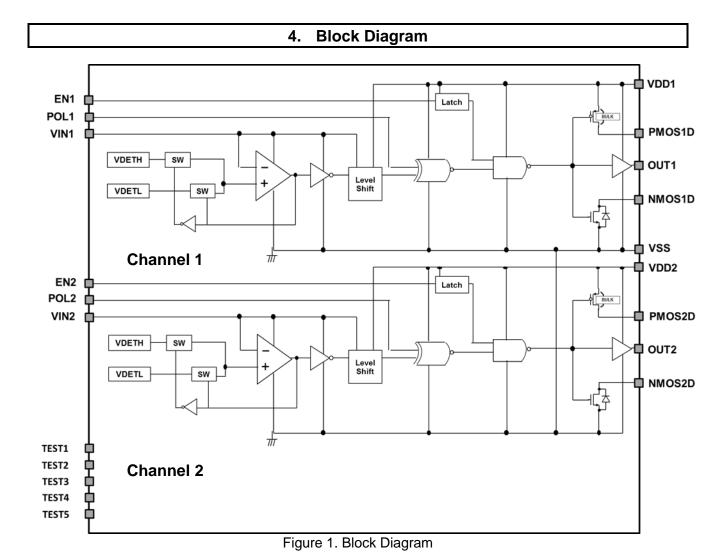

| 4.  | Block Diagram                    |    |

| 5.  | Pin Configuration and Function   |    |

|     |                                  |    |

|     | Function                         | 4  |

| 6.  | Absolute Maximum Ratings         | 5  |

|     | Recommended Operating Conditions |    |

| 8.  | Electrical Characteristics       | 6  |

| 9.  | Description                      |    |

|     |                                  |    |

| 10. |                                  |    |

|     |                                  | 9  |

|     |                                  | 9  |

| 11. |                                  |    |

|     | PORTANT NOTICE                   | 11 |

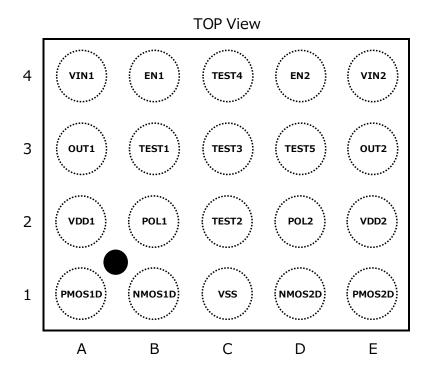

# 5. Pin Configuration and Function

# ■ Pin Configuration

· 20-pin WLCSP

### **■** Function

| WLCSP Pin | Pin Name | I/O               | Function                                                |

|-----------|----------|-------------------|---------------------------------------------------------|

| A1        | PMOS1D   | Input/Output      | PMOS drain pin (Channel 1)                              |

| A2        | VDD1     | Power             | Power supply(Channel 1)                                 |

| A3        | OUT1     | Output            | Logic output (Channel 1)                                |

| A4        | VIN1     | Power             | Detection input pin (Channel 1)                         |

| B1        | NMOS1D   | Output            | NMOS1 drain pin(Channel 1)                              |

| B2        | POL1     | Input             | Polarity cotrol pin (Channel 1)                         |

| B3        | TEST1    | -                 | For test purposes. This pin should be connected to VSS. |

| B4        | EN1      | Input             | Enable pin (Channel 1)                                  |

| C1        | VSS      | Ground            | Ground                                                  |

| C2        | TEST2    | -                 | For test purposes. This pin should be connected to VSS. |

| C3        | TEST3    | -                 | For test purposes. This pin should be connected to VSS. |

| C4        | TEST4    | -                 | For test purposes. This pin should be connected to VSS. |

| D1        | NMOS2D   | Output            | NMOS drain pin(Channel 2)                               |

| D2        | POL2     | Input             | Polarity cotrol pin (Channel 2)                         |

| D3        | TEST5    | -                 | For test purposes. This pin should be connected to VSS. |

| D4        | EN2      | Input             | Enable pin (Channel 2)                                  |

| E1        | PMOS2D   | Input /<br>Output | PMOS drain pin (Channel 2)                              |

| E2        | VDD2     | Power             | Power supply(Channel 2)                                 |

| E3        | OUT2     | Output            | Logic output (Channel 2)                                |

| E4        | VIN2     | Power             | Detection input pin (Channel 2)                         |

### 6. Absolute Maximum Ratings

| Parameter           | Symbol                  | min     | max        | Unit |

|---------------------|-------------------------|---------|------------|------|

|                     | VIN1,VIN2,<br>VDD1,VDD2 | -0.3    | 6.5        | ٧    |

|                     | OUT1,EN1,POL1           | VSS-0.3 | VDD1 + 0.3 | V    |

| Pin Voltage         | OUT2,EN2,POL2           | VSS-0.3 | VDD2 + 0.3 | V    |

| (Note 1)            | PMOS1D<br>PMOS2D        | -0.3    | 6.5        | V    |

|                     | NMOS1D<br>NMOS2D        | -0.3    | 6.5        | V    |

| Power dissipation   | Pd                      | -       | 0.8        | W    |

| Storage Temperature | Temperature Tstg        |         | 150        | °C   |

Note 1. All voltages are with reference to VSS = 0 V.

WARNING: Stresses exceeding Maximum Ratings may damage the device. Normal operation is not guarantee if the condition exceeds the maximum rating.

# 7. Recommended Operating Conditions

| Parameter             | Symbol                       | min | max | Unit |

|-----------------------|------------------------------|-----|-----|------|

| Operation Temperature | Та                           | -40 | 85  | °C   |

| Power Supply Volgtage | VIN1<br>VIN2<br>VDD1<br>VDD2 | 1.2 | 5.5 | V    |

### 8. Electrical Characteristics

(Ta= -40 to 85°C, VIN1, VIN2, VDD1 and VDD2 =1.2V to 5.5V, OUT=open, PMOSD=open, NMOSD=open, unless otherwise specified.)

| Parameter                                  | Symbol                       | min                         | typ        | max                         | Unit | Condition                                                                      |

|--------------------------------------------|------------------------------|-----------------------------|------------|-----------------------------|------|--------------------------------------------------------------------------------|

| Detection Voltage "High"                   | -                            | V <sub>DETH</sub><br>-0.035 | ,          | V <sub>DETH</sub><br>+0.035 | V    | Ta=25°C<br>VIN= "L"→"H"                                                        |

|                                            | VDETH                        | V <sub>DETH</sub><br>-0.045 | $V_{DETH}$ | V <sub>DETH</sub><br>+0.045 | V    | Ta=85°C<br>VIN= "L"→"H"                                                        |

| Detection Voltage "Low"                    | VDETL                        | V <sub>DETL</sub><br>-0.035 | V          | V <sub>DETL</sub><br>+0.035 | V    | Ta=25°C<br>VIN= "H"→"L"                                                        |

|                                            | VDETE                        | V <sub>DETL</sub><br>-0.045 | $V_{DETL}$ | V <sub>DETL</sub><br>+0.045 | V    | Ta=85°C<br>VIN= "H"→"L"                                                        |

| Power Consumption                          | IVIN                         | -                           | 0.026      | 0.050                       | μΑ   | Consumption for VIN per channel while the voltage detection circuit is active. |

|                                            | IVDD<br>(Note 2)<br>(Note 3) | -                           | 0.0001     | 0.100                       | μA   | Consumption for VDD1 and VDD2.                                                 |

| "High"Level Input Voltage                  | VIH                          | VDD<br>×0.8                 | -          | -                           | V    |                                                                                |

| "Low" Level Input Voltage                  | VIL                          | -                           | -          | VDD<br>×0.2                 | V    |                                                                                |

| EN pin reverse current (Push, Pull Note 4) | I <sub>EN</sub>              | 0.15                        |            | -                           | μA   |                                                                                |

| IOH (Note 5)                               | I <sub>OH</sub>              | 0.15                        | -          | -                           | mA   | VIN=V <sub>DETH</sub> +0.1V,<br>OUT=VDD-0.5V                                   |

| IOL(Note 5)                                | I <sub>OL</sub>              | 0.2                         | -          | -                           | mA   | VIN=V <sub>DETL</sub> -0.1V,<br>OUT=0.5V                                       |

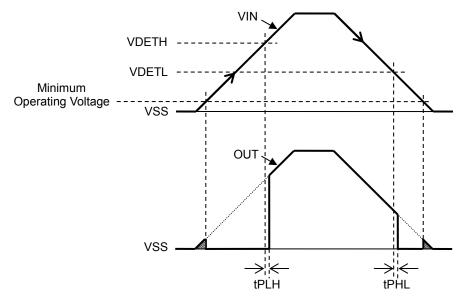

| Response Time (Note 6)                     | tPLH                         | -                           | 0.2        | 0.5                         | ms   | VIN=V <sub>DETH</sub> -0.1V→V <sub>DETH</sub> +0.1V                            |

| (                                          | tPHL                         | -                           | 0.2        | 0.5                         | ms   | VIN= $V_{DETL}$ +0.1V $\rightarrow V_{DETL}$ -0.1V                             |

| P-ch MOSFET<br>On-resistance               | RonP                         | -                           | 1          | 2.3                         | Ω    | VDD≧1.7V                                                                       |

| N-ch MOSFET<br>On-resistance               | RonN                         | -                           | 2          | 5                           | Ω    | VDD≧1.7V                                                                       |

- Note 2. Output drive is not included.

- Note 3. Total power consumption VDD1 and VDD2 (VDD1+VDD2).

- Note 4. EN pin has latch function to keep status. When current comes into or goes out from the EN pin is smaller than the specified value. The AK4110BEC keeps status.

- Note 5. Output current depends on VDD1 and VDD2.

IOL shows N-Channel pull current when AP4410BEC OUT1/OUT2 output low.

IOH shows P-Channel push current when AP4410BEC OUT1/OUT2 output high.

- Note 6. Response time for OUT1 pin and OUT2 pin

#### 9. Description

### Voltage Detection Function

VIN1 pin and VIN2 pin = (Abbreviation; VIN) VDD1 pin and VDD2 pin = (Abbreviation; VDD) POL1 pin and POL2 pin = (Abbreviation; POL) EN1 pin and EN2 pin = (Abbreviation; EN)

#### 1) When the input volgatge is incrasing,

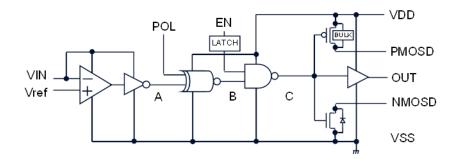

The OUT1 pin and OUT2 pin(Abbreviation;OUT) will be in undefined status when VIN voltage is from VSS to AP4410BEC minimum operating voltage(1.2V). The AP4410BEC internal signal A(Please refer Figure 2) outputs VSS when VIN voltage exceeds minimum operating voltage. When VIN voltage reaches to the detection voltage (VDETH), the internal signal A outputs VIN voltage.

### 2) When the input voltage is decreasing,

When VIN voltage is higher than VDETH, internal signal A outputs VIN. When VIN goes under the detection voltage (VDETL), OUT outputs VSS. The internal signal A will be undefined status when VIN voltage becomes lower than AP4410BEC minimum operating voltage(1.2V).

The logic inputs POL and EN become valid when VDD voltage exceeds 1.2V which is the minimum operation voltage. In case of POL = "L", EN="H", OUT behaves as Figure. 3. The AP4410BEC is able to output the inverted results of the voltage detection using POL. EN can control P-channel MOSFET and N-channel MOSFET ON and OFF. EN has latch function so that it keeps its present state if the input becomes Hi-Z. The BULK of the P-channel MOSFET is connected to the higher voltage pin between VDD and PMOSD.

Figure 2. Block Diagram of Control Logic Part (Each channel)

Figure 3.Function of AP4410BEC voltage detection

Table 1. Control logic truth table (Note 7)

| POL input | VIN                                                                                                                        | EN<br>input | Internal<br>signal A | Internal<br>signal B | Internal<br>signal C | PMOSD | NMOSD | OUT | Note                 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|----------------------|----------------------|-------|-------|-----|----------------------|

| L         | VIN <vdeth< td=""><td>L</td><td>L</td><td>Н</td><td>Н</td><td>OPEN</td><td>L</td><td>Н</td><td>-</td></vdeth<>             | L           | L                    | Н                    | Н                    | OPEN  | L     | Н   | -                    |

| L         | VIN <vdeth< td=""><td>Н</td><td>L</td><td>Н</td><td>L</td><td>Н</td><td>OPEN</td><td>L</td><td>OUT= positive</td></vdeth<> | Н           | L                    | Н                    | L                    | Н     | OPEN  | L   | OUT= positive        |

| L         | VIN≧VDETH                                                                                                                  | Н           | Н                    | L                    | Н                    | OPEN  | L     | Н   | polarity             |

| L         | VIN≧VDETH                                                                                                                  | L           | Н                    | L                    | Н                    | OPEN  | L     | Н   | -                    |

| Н         | VIN <vdeth< td=""><td>L</td><td>L</td><td>L</td><td>Н</td><td>OPEN</td><td>L</td><td>Н</td><td>-</td></vdeth<>             | L           | L                    | L                    | Н                    | OPEN  | L     | Н   | -                    |

| Н         | VIN <vdeth< td=""><td>Н</td><td>L</td><td>L</td><td>Н</td><td>OPEN</td><td>L</td><td>Н</td><td>OUT=</td></vdeth<>          | Н           | L                    | L                    | Н                    | OPEN  | L     | Н   | OUT=                 |

| Н         | VIN≧VDETH                                                                                                                  | Н           | Н                    | Н                    | L                    | Н     | OPEN  | L   | negative<br>polarity |

| Н         | VIN≧VDETH                                                                                                                  | L           | Н                    | Н                    | Н                    | OPEN  | L     | Н   | -                    |

Note 7. When the VIN voltage is incrasing from VDETL or lower.

Table 2 Control logic truth table (Note 8)

| POL input | VIN       | EN<br>input | Internal<br>signal A | Internal<br>signal B | Internal<br>signal C | PMOSD | NMOSD | OUT | Note                 |

|-----------|-----------|-------------|----------------------|----------------------|----------------------|-------|-------|-----|----------------------|

| L         | VIN>VDETL | L           | Н                    | L                    | Н                    | OPEN  | L     | Н   | -                    |

| L         | VIN>VDETL | Н           | Н                    | L                    | Н                    | OPEN  | L     | Н   | OUT= positive        |

| L         | VIN≦VDETL | Н           | L                    | Н                    | L                    | Н     | OPEN  | L   | polarity             |

| L         | VIN≦VDETL | L           | L                    | Н                    | Н                    | OPEN  | L     | Н   | -                    |

| Н         | VIN>VDETL | L           | Н                    | Н                    | П                    | OPEN  | L     | Н   | -                    |

| Н         | VIN>VDETL | Н           | Н                    | Н                    | L                    | Н     | OPEN  | L   | OUT=                 |

| Н         | VIN≦VDETL | Н           | L                    | L                    | Н                    | OPEN  | L     | Н   | negative<br>polarity |

| Н         | VIN≦VDETL | L           | L                    | L                    | Н                    | OPEN  | L     | Н   | -                    |

Note 8. When the VIN voltage is decreasing from VDETH or higher.

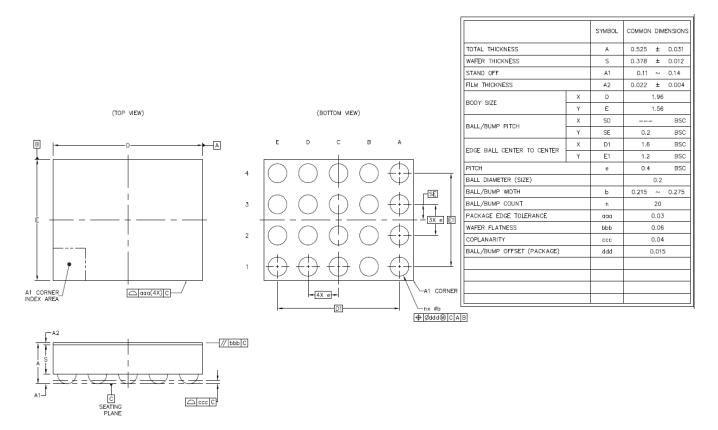

### 10. Package

#### Outline Dimensions

20-pin WLCSP (Unit: mm)

When the IC is exposed to light, it might affect the electrical characteristics of the IC due to the light sensitivity of WLCSP package structures.

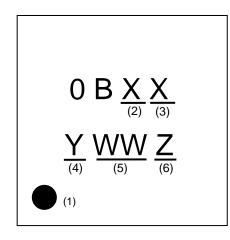

#### Marking

- (1) 1 Pin Indication

- (2) Symbol of the detection voltage of system 1

- (3) Symbol of the detection voltage of system 2

- (4) Year code (last 1 digit)

- (5) Week code

- (6) Management code

| 11.Revision History |

|---------------------|

|---------------------|

| Date (YY/MM/DD) | Revision | Page | Contents          |

|-----------------|----------|------|-------------------|

| 2017/12/18      | 0        | -    | The first edition |

#### IMPORTANT NOTICE

- 0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

- 1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

- 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

- 3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

- 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

- 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

- 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.

Rev 0.0 - 11 - 2017/12